Рачунарски VLSI системи/Питања

Питања на теоријском делу испита се, слично као на РМ1, дохватају из корпуса питања и нису свим студентима иста, али долазе из сличних области. Испод су излистани неки задаци по категоријама питања.

SystemVerilog ограничења

У оваквим задацима, једноставно, је дат SystemVerilog код са ограничењима на неке променљиве, и пита се нешто у вези са вредностима које та променљива може да има и њиховим вероватноћама појављивања.

1. задатак

Које вредности може имати променљива variable из приказане класе Constraints:

class Constraints;

rand bit [3:0] variable;

constraint c1 { variable <= 4'd9; }

constraint c2 { variable inside {[4:14]}; }

constraint c3 { ! (variable inside {4'h0, 4'h5}); }

endclass

Могуће вредности, сортиране од најмање ка највећој, у децималном бројном систему, раздвојене запетом без пратећег размака, навести као одговор.

Напомена: Приказ очекиваног формата одговора за следеће произвољно одабране вредности 15, 2, 7 и 10 јесте:

2,7,10,15

Одговор: 4,6,7,8,9

2. задатак

Дата је класа Constraints:

class Constraints;

rand bit [2:0] variable;

constraint distribution { variable dist { 0:/20, 1:/30, [2:6]:/40, 7:/10 }; }

endclass

Која је вероватноћа да променљива variable приликом генерисања псеудослучајне вредности добије вредност 4? Вероватноћу представити као разломак у којем су бројилац и именилац узајамно прости бројеви.

- Бројилац: 2

- Именилац: 25

3. задатак

Које вредности може имати променљива v2 из приказане класе Constraints:

class Constraints;

randc bit [3:0] v1;

randc bit [3:0] v2;

constraint c1 { v1 > 4'b0100; }

constraint c2 { ! (v1 inside {[4'h8:4'hF]}); }

constraint c3 { v2 == v1 * 2 + 1; }

endclass

Могуће вредности, сортиране од најмање ка највећој, у децималном бројном систему, раздвојене запетом без пратећег размака, навести као одговор.

Напомена: Приказ очекиваног формата одговора за следеће произвољно одабране вредности 15, 2, 7 и 10 јесте:

2,7,10,15

Одговор: 11,13,15

4. задатак

Дата је класа Constraints:

class Constraints;

rand bit [2:0] variable;

constraint distribution { variable dist { 0:/20, 1:/30, [2:6]:/20, 7:/30 }; }

endclass

Која је вероватноћа да променљива variable приликом генерисања псеудослучајне вредности добије вредност 4? Вероватноћу представити као разломак у којем су бројилац и именилац узајамно прости бројеви.

- Бројилац: 1

- Именилац: 25

5. задатак

Дата је класа Constraints:

class Constraints;

rand bit [2:0] variable;

constraint distribution { variable dist { 0:/20, 1:/30, [2:6]:=20, 7:/30 }; }

endclass

Која је вероватноћа да променљива variable приликом генерисања псеудослучајне вредности добије вредност 4? Вероватноћу представити као разломак у којем су бројилац и именилац узајамно прости бројеви.

- Бројилац: 1

- Именилац: 9

Objašnjenje: Kada stoji := to znači da se svakom broju iz opsega dodeljuje ta verovatnoća, za razliku od :/ koji označava kumulativnu verovatnoću za ceo opseg. Samim tim ukupna verovatnoća je , verovatnoća za broj 4 je 20, tako da će rezultat biti čijim skraćivanjem se dobija traženo rešenje.

Сабирачи

У оваквим задацима обично је дат Verilog код одређеног сабирача (једног од типова као што су рађени на предавањима) и питају се ствари у вези са функционисањем тог сабирача.

1. задатак

У наставку је дата имплементација једног осморазредног сабирача. О ком сабирачу се ради, ако се зна да модул ripple_carry_adder_n представља N-разредни сабирач са серијским преносом, а да модул multiplexer_2_1 представља двоулазни мултиплексер ширине N информационих улаза?

module adder_8 (

input [7:0] a, b,

input carry_in,

output [7:0] sum,

output carry_out

);

wire carry_3_0, carry_3_1, carry_3;

wire [3:0] sum_low_0, sum_low_1, sum_low;

ripple_carry_adder_n #(4) rca_1 (a[3:0], b[3:0], 1'b0, sum_low_0, carry_3_0);

ripple_carry_adder_n #(4) rca_2 (a[3:0], b[3:0], 1'b1, sum_low_1, carry_3_1);

multiplexer_2_1 #(4) mpx_1 (sum_low_0, sum_low_1, carry_in, sum_low);

assign carry_3 = (carry_in & carry_3_1) | carry_3_0;

wire carry_7_0, carry_7_1, carry_7;

wire [3:0] sum_high_0, sum_high_1, sum_high;

ripple_carry_adder_n #(4) rca_3 (a[7:4], b[7:4], 1'b0, sum_high_0, carry_7_0);

ripple_carry_adder_n #(4) rca_4 (a[7:4], b[7:4], 1'b1, sum_high_1, carry_7_1);

multiplexer_2_1 #(4) mpx_2 (sum_high_0, sum_high_1, carry_3, sum_high);

assign carry_7 = carry_7_0 | (carry_3_0 & carry_7_1) | (carry_in & carry_3_1 & carry_7_1);

assign sum = {sum_high, sum_low};

assign carry_out = carry_7;

endmodule

- Условни сабирач (Conditional Sum Adder)

- Сабирач са серијским преносом (Ripple Carry Adder)

- Сабирач са чувањем преноса (Carry Save Adder)

- Сабирач на основу бита преноса (Carry Select Adder)

- Сабирач са паралелним преносом (Carry Lookahead Adder)

- Потпуни сабирач (Full Adder)

Објашњење: У коду се види карактеристични "осакаћени мултиплексер" код генерисања преноса carry_3 и carry_7.

2. задатак

У наставку је дата непотпуна имплементација четвороразредног сабирача на основу бита преноса (Carry Select Adder). Допунити имплементацију, ако се зна да модул ripple_carry_adder_n представља N-разредни сабирач са серијским преносом, а да модул multiplexer_2_1 представља двоулазни мултиплексер ширине N информационих улаза?[sic]

module carry_select_adder_4 (

input [3:0] a, b,

input carry_in,

output [3:0] sum,

output carry_out

);

wire carry_3_0, carry_3_1;

wire [3:0] sum_0, sum_1;

ripple_carry_adder_n #(4) rca_1 (a[3:0], b[3:0], БЕЛИНА_1, sum_0, БЕЛИНА_2);

ripple_carry_adder_n #(4) rca_2 (a[3:0], b[3:0], БЕЛИНА_3, sum_1, БЕЛИНА_4);

multiplexer_2_1 #(4) mpx_1 (sum_0, sum_1, carry_in, sum);

assign carry_out = (carry_in & carry_3_1) | carry_3_0;

endmodule

- Белина 1: 1'b0

- Белина 2: carry_3_0

- Белина 3: 1'b1

- Белина 4: carry_3_1

Објашњење: Ово је само друга варијанта задатка изнад. Једном сабирачу се даје да рачуна као да је улазни пренос 0, а другом да је улазни пренос 1, па се њихови резултати смештају у одговарајуће сигнале.

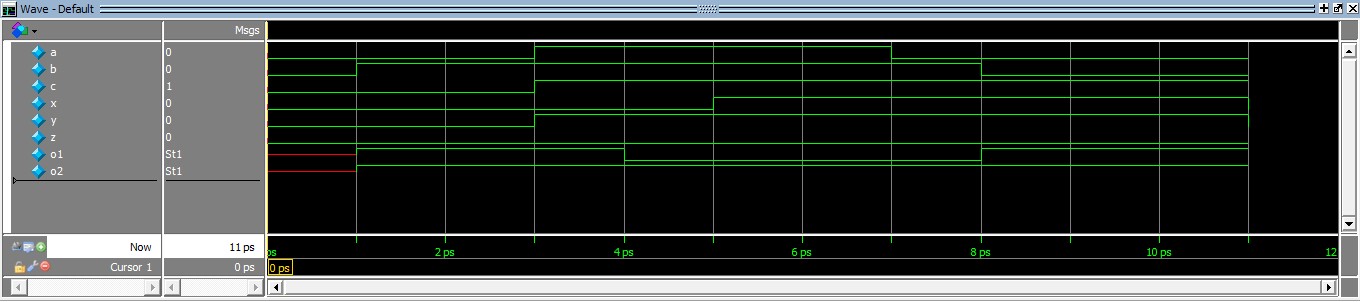

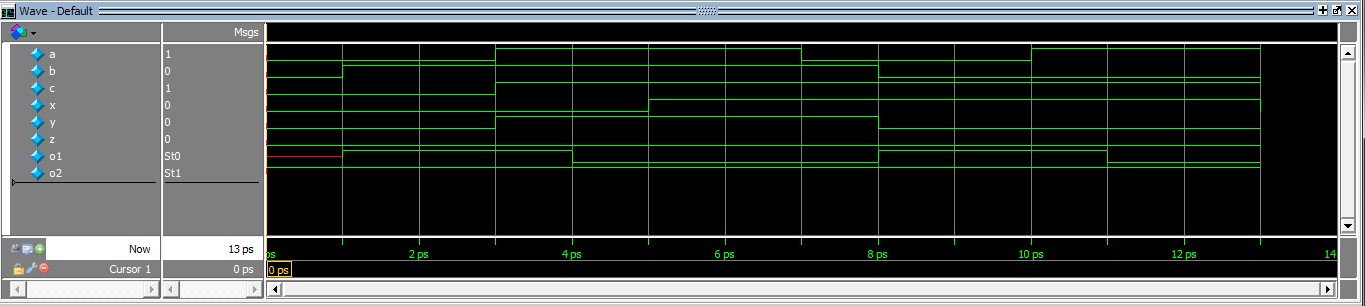

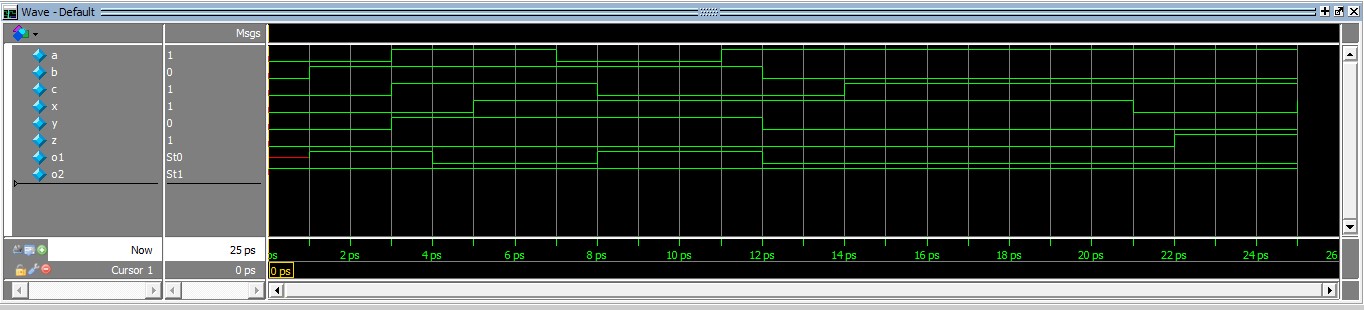

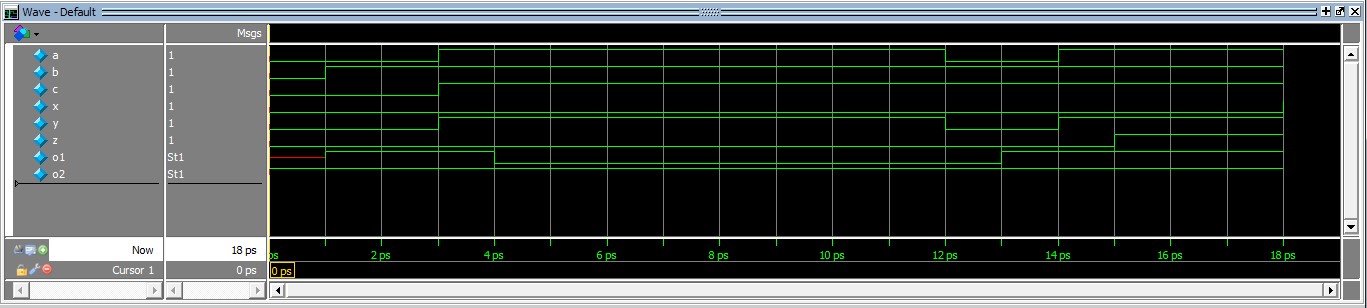

Временски облици

У оваквим задацима дат је Verilog код са кашњењима и временски облици излазних сигнала у ModelSim, па се студенти питају да препознају одговарајући временски облик.

1. задатак

- Овај задатак није решен. Помозите SI Wiki тако што ћете га решити.

Који временски облик одговара следећем изворном коду:

module delay_module_3 (

out1, out2, a, b, c, x, y, z

);

output reg out1, out2;

input a, b, c, x, y, z;

wire e, f, g;

always @(posedge a) out1 = #1 b & c;

always @(negedge a) out1 = #1 b | ~c;

always @(posedge x) out2 = #1 y ^ z;

always @(negedge x) out2 = #1 ~y;

endmodule

module top_display;

reg a, b, c, x, y, z;

wire o1, o2;

delay_module_3 d3(o1, o2, a, b, c, x, y, z);

initial begin

a = 1'b0; b = 1'b0; c = 1'b0; x = 1'b0; y = 1'b0; z = 1'b0;

#1 b = 1'b1;

#2 a = 1'b1; y = 1'b1;

#0 c = 1'b1;

#2 x = 1'b1;

#2 a = 1'b0;

#1 b = 1'b0;

#3 x = 1'b0;

#0 y = 1'b0;

#0 $finish;

end

endmodule

- Ниједан од понуђених временских облика.

Померачи

У оваквим задацима дат је Фанел или Барел померач са одређеним карактеристикама, и траже се сви његови међурезултати.

1. задатак

Дат је Фанел померач (Funnel Shifter) са дванаестобитним улазом и петобитним излазом. Допунити вредности добијене у сваком од корака овог померача као и вредност излзаног податка за следеће улазне вредности:

- Улазни податак: 5A7

- Контролни сигнал (број померања удесно): 4

- Први корак: 5A

- Други корак: 1A

- Трећи корак: 1A

- Излазни податак: 1A

Све вредности су написане у хексадецималном бројном систему.

2. задатак

Дат је Барел померач (Barrel Shifter) са осмобитним улазом и осмобитним излазом. Допунити вредности добијене у сваком од корака овог померача као и вредност излзаног податка за следеће улазне вредности:

- Улазни податак: 79

- Контролни сигнал (број померања удесно): 7

- Први корак: 97

- Други корак: E5

- Трећи корак: F2

- Излазни податак: F2

Све вредности су написане у хексадецималном бројном систему.

3. задатак [фебруар 2024 - група 1]

Дат је Фанел померач (Funnel Shifter) са дванаестобитним улазом и петобитним излазом. Допунити вредности добијене у сваком од корака овог померача као и вредност излзаног податка за следеће улазне вредности:

- Улазни податак: 26D

- Контролни сигнал (број померања удесно): 5

- Први корак: 26

- Други корак: 26

- Трећи корак: 13

- Излазни податак: 13

Све вредности су написане у хексадецималном бројном систему.

4. задатак [фебруар 2024 - група 2]

Дат је Фанел померач (Funnel Shifter) са дванаестобитним улазом и петобитним излазом. Допунити вредности добијене у сваком од корака овог померача као и вредност излзаног податка за следеће улазне вредности:

- Улазни податак: 3F8

- Контролни сигнал (број померања удесно): 7

- Први корак: 3F

- Други корак: E

- Трећи корак: 7

- Излазни податак: 7

Све вредности су написане у хексадецималном бројном систему.

Верификација без UVM

У оваквим задацима дат је код из примера верификације без коришћења UVM стандарда са вежби и пита се шта се тачно дешава у коду и зашто.

1. задатак

У наставку је дат део кода Driver-a.

class Driver;

virtual reg8_if vif;

mailbox mbx;

event done;

task run();

@(posedge vif.clk);

forever begin

dut_item item;

mbx.get(item);

// ...

@(posedge vif.clk);

->done;

end

endtask

endclass

Koja класа чека на догађај done који се овде окида?

Напомена: Сматрати да се процес верификације врши без коришћења UVM стандарда.

- Driver

- Generator

- Monitor

- Scoreboard

Објашњење: Први пример са вежби. Генератор чека на овај догађај како не би генерисао више предмета него што драјвер може да конзумира.

2. задатак

У наставку је дат део кода Driver-a.

class Driver;

virtual reg8_if vif;

mailbox mbx;

event done;

task run();

@(posedge vif.clk);

forever begin

dut_item item;

mbx.get(item);

// ...

@(posedge vif.clk);

->done;

end

endtask

endclass

Koja класа поставља item у mailbox који се овде дохвата?

Напомена: Сматрати да се процес верификације врши без коришћења UVM стандарда.

- Driver

- Generator

- Monitor

- Scoreboard

UVM

Ова питања се обично односе на било шта из UVM стандарда.

1. задатак

Које класе наслеђују класу uvm_transaction?

uvm_sequence_itemuvm_driveruvm_monitoruvm_sequenceruvm_testuvm_sequence

2. задатак

Које фазе кроз које пролазе UVM компоненте се реализују као task уместо као функције?

- build

- connect

- end of elaboration

- start of simulation

- run

- extract

- check

- report