Računarski VLSI sistemi/Pitanja

Pitanja na teorijskom delu ispita se, slično kao na RM1, dohvataju iz korpusa pitanja i nisu svim studentima ista, ali dolaze iz sličnih oblasti. Ispod su izlistani neki zadaci po kategorijama pitanja.

SystemVerilog ograničenja

U ovakvim zadacima, jednostavno, je dat SystemVerilog kod sa ograničenjima na neke promenljive, i pita se nešto u vezi sa vrednostima koje ta promenljiva može da ima i njihovim verovatnoćama pojavljivanja.

Zadatak 1

Koje vrednosti može imati promenljiva variable iz prikazane klase Constraints:

class Constraints;

rand bit [3:0] variable;

constraint c1 { variable <= 4'd9; }

constraint c2 { variable inside {[4:14]}; }

constraint c3 { ! (variable inside {4'h0, 4'h5}); }

endclass

Moguće vrednosti, sortirane od najmanje ka najvećoj, u decimalnom brojnom sistemu, razdvojene zapetom bez pratećeg razmaka, navesti kao odgovor.

Napomena: Prikaz očekivanog formata odgovora za sledeće proizvoljno odabrane vrednosti 15, 2, 7 i 10 jeste:

2,7,10,15

Odgovor: 4,6,7,8,9

Zadatak 2

- Ovaj zadatak nije rešen. Pomozite SI Wiki tako što ćete ga rešiti.

Data je klasa Constraints:

class Constraints;

rand bit [2:0] variable;

constraint distribution { variable dist { 0:/20, 1:/30, [2:6]:/40, 7:/10 }; }

endclass

Koja je verovatnoća da promenljiva variable prilikom generisanja pseudoslučajne vrednosti dobije vrednost 4? Verovatnoću predstaviti kao razlomak u kojem su brojilac i imenilac uzajamno prosti brojevi.

- Brojilac: nerešeno

- Imenilac: nerešeno

Sabirači

U ovakvim zadacima obično je dat Verilog kod određenog sabirača (jednog od tipova kao što su rađeni na predavanjima) i pitaju se stvari u vezi sa funkcionisanjem tog sabirača.

Zadatak 1

U nastavku je data implementacija jednog osmorazrednog sabirača. O kom sabiraču se radi, ako se zna da modul ripple_carry_adder_n predstavlja N-razredni sabirač sa serijskim prenosom, a da modul multiplexer_2_1 predstavlja dvoulazni multiplekser širine N informacionih ulaza?

module adder_8 (

input [7:0] a, b,

input carry_in,

output [7:0] sum,

output carry_out

);

wire carry_3_0, carry_3_1, carry_3;

wire [3:0] sum_low_0, sum_low_1, sum_low;

ripple_carry_adder_n #(4) rca_1 (a[3:0], b[3:0], 1'b0, sum_low_0, carry_3_0);

ripple_carry_adder_n #(4) rca_2 (a[3:0], b[3:0], 1'b1, sum_low_1, carry_3_1);

multiplexer_2_1 #(4) mpx_1 (sum_low_0, sum_low_1, carry_in, sum_low);

assign carry_3 = (carry_in & carry_3_1) | carry_3_0;

wire carry_7_0, carry_7_1, carry_7;

wire [3:0] sum_high_0, sum_high_1, sum_high;

ripple_carry_adder_n #(4) rca_3 (a[7:4], b[7:4], 1'b0, sum_high_0, carry_7_0);

ripple_carry_adder_n #(4) rca_4 (a[7:4], b[7:4], 1'b1, sum_high_1, carry_7_1);

multiplexer_2_1 #(4) mpx_2 (sum_high_0, sum_high_1, carry_3, sum_high);

assign carry_7 = carry_7_0 | (carry_3_0 & carry_7_1) | (carry_in & carry_3_1 & carry_7_1);

assign sum = {sum_high, sum_low};

assign carry_out = carry_7;

endmodule

- Uslovni sabirač (Conditional Sum Adder)

- Sabirač sa serijskim prenosom (Ripple Carry Adder)

- Sabirač sa čuvanjem prenosa (Carry Save Adder)

- Sabirač na osnovu bita prenosa (Carry Select Adder)

- Sabirač sa paralelnim prenosom (Carry Lookahead Adder)

- Potpuni sabirač (Full Adder)

Objašnjenje: U kodu se vidi karakteristični "osakaćeni multiplekser" kod generisanja prenosa carry_3 i carry_7.

Zadatak 2

U nastavku je data nepotpuna implementacija četvororazrednog sabirača na osnovu bita prenosa (Carry Select Adder). Dopuniti implementaciju, ako se zna da modul ripple_carry_adder_n predstavlja N-razredni sabirač sa serijskim prenosom, a da modul multiplexer_2_1 predstavlja dvoulazni multiplekser širine N informacionih ulaza?[sic]

module carry_select_adder_4 (

input [3:0] a, b,

input carry_in,

output [3:0] sum,

output carry_out

);

wire carry_3_0, carry_3_1;

wire [3:0] sum_0, sum_1;

ripple_carry_adder_n #(4) rca_1 (a[3:0], b[3:0], БЕЛИНА_1, sum_0, БЕЛИНА_2);

ripple_carry_adder_n #(4) rca_2 (a[3:0], b[3:0], БЕЛИНА_3, sum_1, БЕЛИНА_4);

multiplexer_2_1 #(4) mpx_1 (sum_0, sum_1, carry_in, sum);

assign carry_out = (carry_in & carry_3_1) | carry_3_0;

endmodule

- Belina 1: 1'b0

- Belina 2: carry_3_0

- Belina 3: 1'b1

- Belina 4: carry_3_1

Objašnjenje: Ovo je samo druga varijanta zadatka iznad. Jednom sabiraču se daje da računa kao da je ulazni prenos 0, a drugom da je ulazni prenos 1, pa se njihovi rezultati smeštaju u odgovarajuće signale.

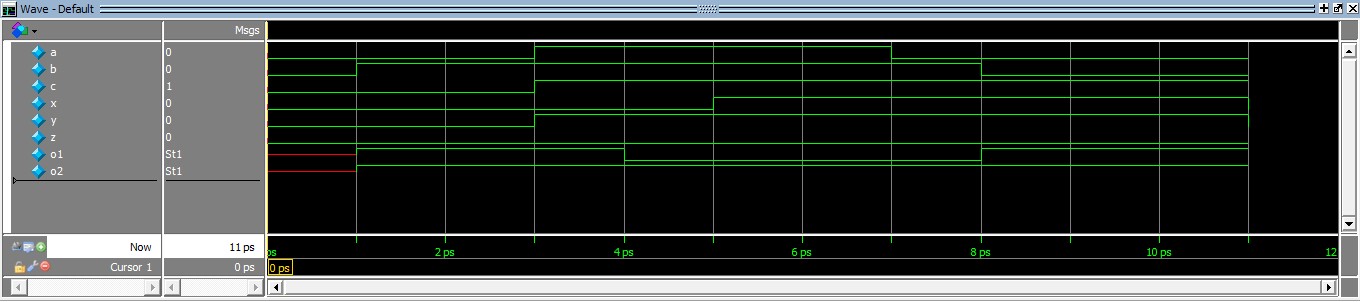

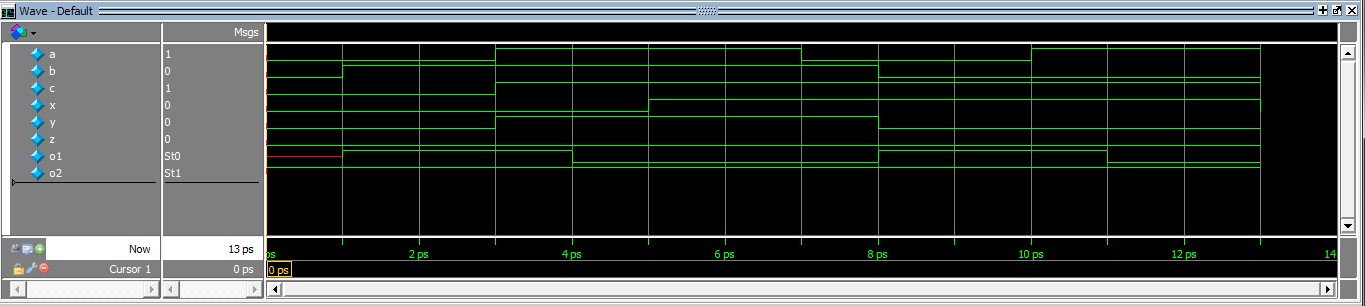

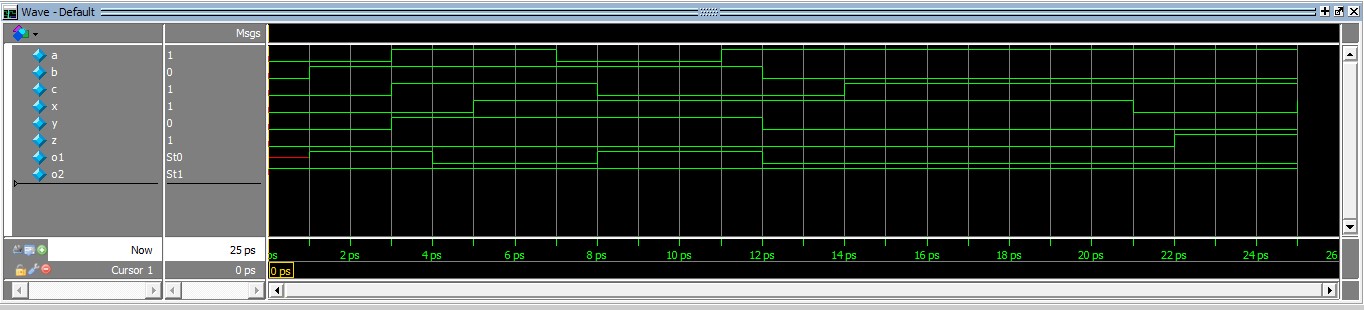

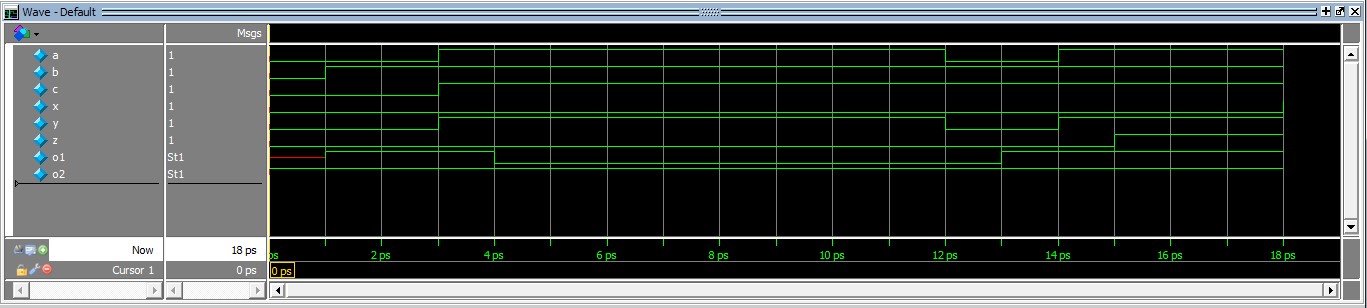

Vremenski oblici

U ovakvim zadacima dat je Verilog kod sa kašnjenjima i vremenski oblici izlaznih signala u ModelSim, pa se studenti pitaju da prepoznaju odgovarajući vremenski oblik.

Zadatak 1

- Ovaj zadatak nije rešen. Pomozite SI Wiki tako što ćete ga rešiti.

Koji vremenski oblik odgovara sledećem izvornom kodu:

module delay_module_3 (

out1, out2, a, b, c, x, y, z

);

output reg out1, out2;

input a, b, c, x, y, z;

wire e, f, g;

always @(posedge a) out1 = #1 b & c;

always @(negedge a) out1 = #1 b | ~c;

always @(posedge x) out2 = #1 y ^ z;

always @(negedge x) out2 = #1 ~y;

endmodule

module top_display;

reg a, b, c, x, y, z;

wire o1, o2;

delay_module_3 d3(o1, o2, a, b, c, x, y, z);

initial begin

a = 1'b0; b = 1'b0; c = 1'b0; x = 1'b0; y = 1'b0; z = 1'b0;

#1 b = 1'b1;

#2 a = 1'b1; y = 1'b1;

#0 c = 1'b1;

#2 x = 1'b1;

#2 a = 1'b0;

#1 b = 1'b0;

#3 x = 1'b0;

#0 y = 1'b0;

#0 $finish;

end

endmodule

- Nijedan od ponuđenih vremenskih oblika.

Pomerači

U ovakvim zadacima dat je Fanel ili Barel pomerač sa određenim karakteristikama, i traže se svi njegovi međurezultati.

Zadatak 1

Dat je Fanel pomerač (Funnel Shifter) sa dvanaestobitnim ulazom i petobitnim izlazom. Dopuniti vrednosti dobijene u svakom od koraka ovog pomerača kao i vrednost izlzanog podatka za sledeće ulazne vrednosti:

- Ulazni podatak: 5A7

- Kontrolni signal (broj pomeranja udesno): 4

- Prvi korak: 5A

- Drugi korak: 5A

- Treći korak: 1A

- Izlazni podatak: 1A

Sve vrednosti su napisane u heksadecimalnom brojnom sistemu.

Zadatak 2

- Ovaj zadatak nije rešen. Pomozite SI Wiki tako što ćete ga rešiti.

Dat je Barel pomerač (Barrel Shifter) sa osmobitnim ulazom i osmobitnim izlazom. Dopuniti vrednosti dobijene u svakom od koraka ovog pomerača kao i vrednost izlzanog podatka za sledeće ulazne vrednosti:

- Ulazni podatak: 79

- Kontrolni signal (broj pomeranja udesno): 7

- Prvi korak: nerešeno

- Drugi korak: nerešeno

- Treći korak: nerešeno

- Izlazni podatak: nerešeno

Sve vrednosti su napisane u heksadecimalnom brojnom sistemu.

Verifikacija bez UVM

U ovakvim zadacima dat je kod iz primera verifikacije bez korišćenja UVM standarda sa vežbi i pita se šta se tačno dešava u kodu i zašto.

Zadatak 1

U nastavku je dat deo koda Driver-a.

class Driver;

virtual reg8_if vif;

mailbox mbx;

event done;

task run();

@(posedge vif.clk);

forever begin

dut_item item;

mbx.get(item);

// ...

@(posedge vif.clk);

->done;

end

endtask

endclass

Koja klasa čeka na događaj done koji se ovde okida?

Napomena: Smatrati da se proces verifikacije vrši bez korišćenja UVM standarda.

- Driver

- Generator

- Monitor

- Scoreboard

Objašnjenje: Prvi primer sa vežbi. Generator čeka na ovaj događaj kako ne bi generisao više predmeta nego što drajver može da konzumira.

Zadatak 2

U nastavku je dat deo koda Driver-a.

class Driver;

virtual reg8_if vif;

mailbox mbx;

event done;

task run();

@(posedge vif.clk);

forever begin

dut_item item;

mbx.get(item);

// ...

@(posedge vif.clk);

->done;

end

endtask

endclass

Koja klasa postavlja item u mailbox koji se ovde dohvata?

Napomena: Smatrati da se proces verifikacije vrši bez korišćenja UVM standarda.

- Driver

- Generator

- Monitor

- Scoreboard